- Bài viết

- 1,972

- Điểm tương tác

- 166

- Điểm

- 63

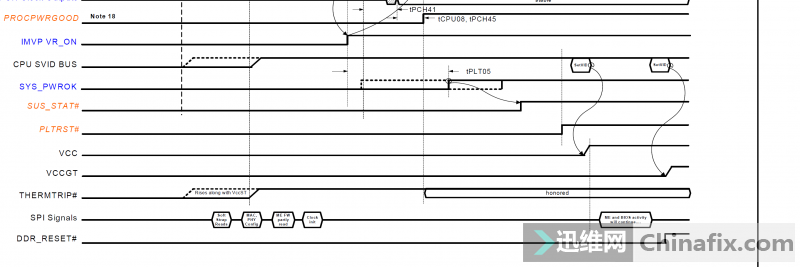

Giới thiệu tóm tắt về quy trình làm việc của bo mạch chủ z490

Quy trình kiểm tra sửa chữa:

1. Trước khi cắm nguồn, pin cúc áo 3V được chuyển đổi thành điện áp VCC của mạch RTC của cầu nối thông qua mạch điện.

2. Pin 3V cung cấp điện áp rtcrst mức cao cho cầu sau khi chuyển đổi mạch và nhảy mũ CMOS#.

3. Cầu làm rung Crystal, VCC và Crystal và tạo ra tần số 32.768KHz cho cầu.

4. Cắm ATX và xuất ra 5VSB bằng dây màu tím.

5. 5VSB thường được bộ điều chỉnh điện áp chuyển đổi để tạo ra VCC chờ ngủ sâu 3,3V cho IO và Bridge (vccdsw ﹤ 3p3).

Sau khi IO phát hiện VCC bình thường, nó sẽ gửi VCC chờ ngủ sâu để kết nối (DSW? Pwrok).

Cầu gửi lệnh điều khiển SLP_Sus để tạo VCC dự phòng chính (vccprim š 3p3, vccprim Ŧ 1p8, vccprim ා 1p05).

Nguồn VCC dự phòng chính 3,3V cung cấp khe cắm PCIe, card mạng, IO và cầu nối.

Cầu nối đọc BIOS và cấu hình bit chân.

6. Nói chung, sau khi IO phát hiện VCC dự phòng bình thường, nó sẽ gửi VCC dự phòng tốt (rsmrst ා) đến cầu nối.

7.Công tắc, Công tắc, IO đầu vào.

8. IO gửi tín hiệu yêu cầu cấp nguồn tới cầu nối (pwrbtn ා).

9. Cầu gửi tín hiệu SLP_S *, trong đó SLP_S3 tới IO.

Hoặc cầu nối gửi tín hiệu cho phép bạn khởi động máy đến IO thông qua bus ESPI.

10. IO hạ thấp đường màu xanh lá cây của ATX (pson ා).

Chế độ khởi động VCC của ESPI được cho phép, tất cả các kênh của ESPI sẽ gửi tín hiệu.

11. Điện áp đầu ra 12V / 5V / 3.3V / – 12V.

12、SLP_S4 ා đầu tiên điều khiển việc tạo ra vpp2.5v và ᦇ 1.05v ᦇ vccstpll, sau đó chuyển đổi điều khiển để tạo ra bộ nhớ chính VCC 1.2v.

13、SLP_S3 ා điều khiển việc tạo ra điện áp vccstg 1,05v.

SLP_Sau khi S3 ා và bộ nhớ VCC bình thường, bộ điều khiển sẽ tạo ra VCC 0,95v vccio và VCC 1,05v vccsa.

14. Sau khi VCC ở trên trở lại bình thường, quá trình chuyển đổi sẽ tạo ra EN của CPU VCC.

Nhưng nó sẽ không tạo ra CPU VCC, vboot = 0V.

15. Chip CPU VCC gửi tín hiệu đến PCH của bridge_Pwrok, cho biết chip đã sẵn sàng tạo CPU VCC.

16. PG của đường màu xám được gửi đến IO bằng độ trễ nguồn ATX.

17. Sau khi IO phát hiện VCC và atxpg bình thường, nó sẽ gửi PG đến sys của bridge_PWROK.

18. Rung động ban đầu của cầu là 24m.

19. Cầu nối gửi tín hiệu CLK và cpupwrgd tới CPU.

20. Cầu gửi lệnh reset nền tảng đầu tiên tới IO, IO gửi lệnh reset tới card mạng, PCIe, v.v.

21. Cầu gửi lệnh reset CPU của CPU_RST#.

CPU gửi tín hiệu SVID tới chip CPU VCC.

Chip điều khiển CPU VCC đầu ra CPU VCC/ điều chỉnh CPU VCC đến giá trị phù hợp với CPU hiện tại.

Bắt đầu đọc CPU và chạy mã BIOS.

Sau khi z490 tự kiểm tra bộ nhớ, CPU sẽ gửi SVID thứ hai và điều khiển việc tạo VCC vccg hiển thị tập trung.

Giới thiệu quy trình làm việc của bo mạch chủ Z490 Hình 1.

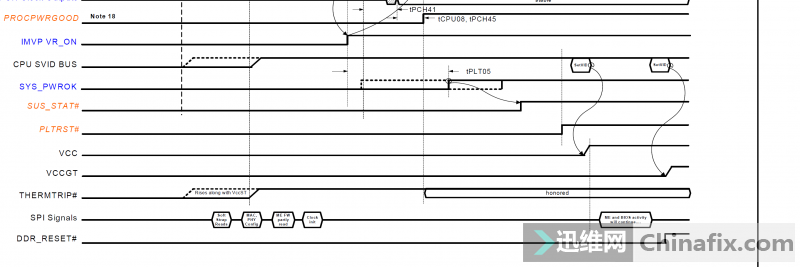

Quy trình kiểm tra sửa chữa:

1. Trước khi cắm nguồn, pin cúc áo 3V được chuyển đổi thành điện áp VCC của mạch RTC của cầu nối thông qua mạch điện.

2. Pin 3V cung cấp điện áp rtcrst mức cao cho cầu sau khi chuyển đổi mạch và nhảy mũ CMOS#.

3. Cầu làm rung Crystal, VCC và Crystal và tạo ra tần số 32.768KHz cho cầu.

4. Cắm ATX và xuất ra 5VSB bằng dây màu tím.

5. 5VSB thường được bộ điều chỉnh điện áp chuyển đổi để tạo ra VCC chờ ngủ sâu 3,3V cho IO và Bridge (vccdsw ﹤ 3p3).

Sau khi IO phát hiện VCC bình thường, nó sẽ gửi VCC chờ ngủ sâu để kết nối (DSW? Pwrok).

Cầu gửi lệnh điều khiển SLP_Sus để tạo VCC dự phòng chính (vccprim š 3p3, vccprim Ŧ 1p8, vccprim ා 1p05).

Nguồn VCC dự phòng chính 3,3V cung cấp khe cắm PCIe, card mạng, IO và cầu nối.

Cầu nối đọc BIOS và cấu hình bit chân.

6. Nói chung, sau khi IO phát hiện VCC dự phòng bình thường, nó sẽ gửi VCC dự phòng tốt (rsmrst ා) đến cầu nối.

7.Công tắc, Công tắc, IO đầu vào.

8. IO gửi tín hiệu yêu cầu cấp nguồn tới cầu nối (pwrbtn ා).

9. Cầu gửi tín hiệu SLP_S *, trong đó SLP_S3 tới IO.

Hoặc cầu nối gửi tín hiệu cho phép bạn khởi động máy đến IO thông qua bus ESPI.

10. IO hạ thấp đường màu xanh lá cây của ATX (pson ා).

Chế độ khởi động VCC của ESPI được cho phép, tất cả các kênh của ESPI sẽ gửi tín hiệu.

11. Điện áp đầu ra 12V / 5V / 3.3V / – 12V.

12、SLP_S4 ා đầu tiên điều khiển việc tạo ra vpp2.5v và ᦇ 1.05v ᦇ vccstpll, sau đó chuyển đổi điều khiển để tạo ra bộ nhớ chính VCC 1.2v.

13、SLP_S3 ා điều khiển việc tạo ra điện áp vccstg 1,05v.

SLP_Sau khi S3 ා và bộ nhớ VCC bình thường, bộ điều khiển sẽ tạo ra VCC 0,95v vccio và VCC 1,05v vccsa.

14. Sau khi VCC ở trên trở lại bình thường, quá trình chuyển đổi sẽ tạo ra EN của CPU VCC.

Nhưng nó sẽ không tạo ra CPU VCC, vboot = 0V.

15. Chip CPU VCC gửi tín hiệu đến PCH của bridge_Pwrok, cho biết chip đã sẵn sàng tạo CPU VCC.

16. PG của đường màu xám được gửi đến IO bằng độ trễ nguồn ATX.

17. Sau khi IO phát hiện VCC và atxpg bình thường, nó sẽ gửi PG đến sys của bridge_PWROK.

18. Rung động ban đầu của cầu là 24m.

19. Cầu nối gửi tín hiệu CLK và cpupwrgd tới CPU.

20. Cầu gửi lệnh reset nền tảng đầu tiên tới IO, IO gửi lệnh reset tới card mạng, PCIe, v.v.

21. Cầu gửi lệnh reset CPU của CPU_RST#.

CPU gửi tín hiệu SVID tới chip CPU VCC.

Chip điều khiển CPU VCC đầu ra CPU VCC/ điều chỉnh CPU VCC đến giá trị phù hợp với CPU hiện tại.

Bắt đầu đọc CPU và chạy mã BIOS.

Sau khi z490 tự kiểm tra bộ nhớ, CPU sẽ gửi SVID thứ hai và điều khiển việc tạo VCC vccg hiển thị tập trung.

Giới thiệu quy trình làm việc của bo mạch chủ Z490 Hình 1.